54, 74 Series Noise Cancellation GHz Logic

QUADRUPLE 2-INPUT POSITIVE-NAND GATE

INPUTS

OUTPUT

Y

A

B

H

H

L

L

X

H

X

L

H

FEATURES:

. Patented technology

. Specified From –40°C to 85°C, –40°C to 125°C,

and –55°C to 125°C

. Operating frequency up to 1.125GHz with 2pf load

. Operating frequency up to 750MHz with 5pf load

. Operating frequency up to 350MHz with 15pf load

. V

CC

Operates from 1.65V to 3.6V

. Propagation delay < 1.5ns max with 15pf load

. Low input capacitance: 4pf typical

. Latch-Up Performance Exceeds 250 mA Per

JESD 17

. ESD Protection Exceeds JESD 22

. 5000-VHuman-BodyModel (A114-A)

. 200-VMachineModel (A115-A)

. Available in 14pin 150mil wide SOIC package

. Available in 14pin Ceramic Dual Flatpack

. Available in 20pin Leadless Ceramic Chip Carrier

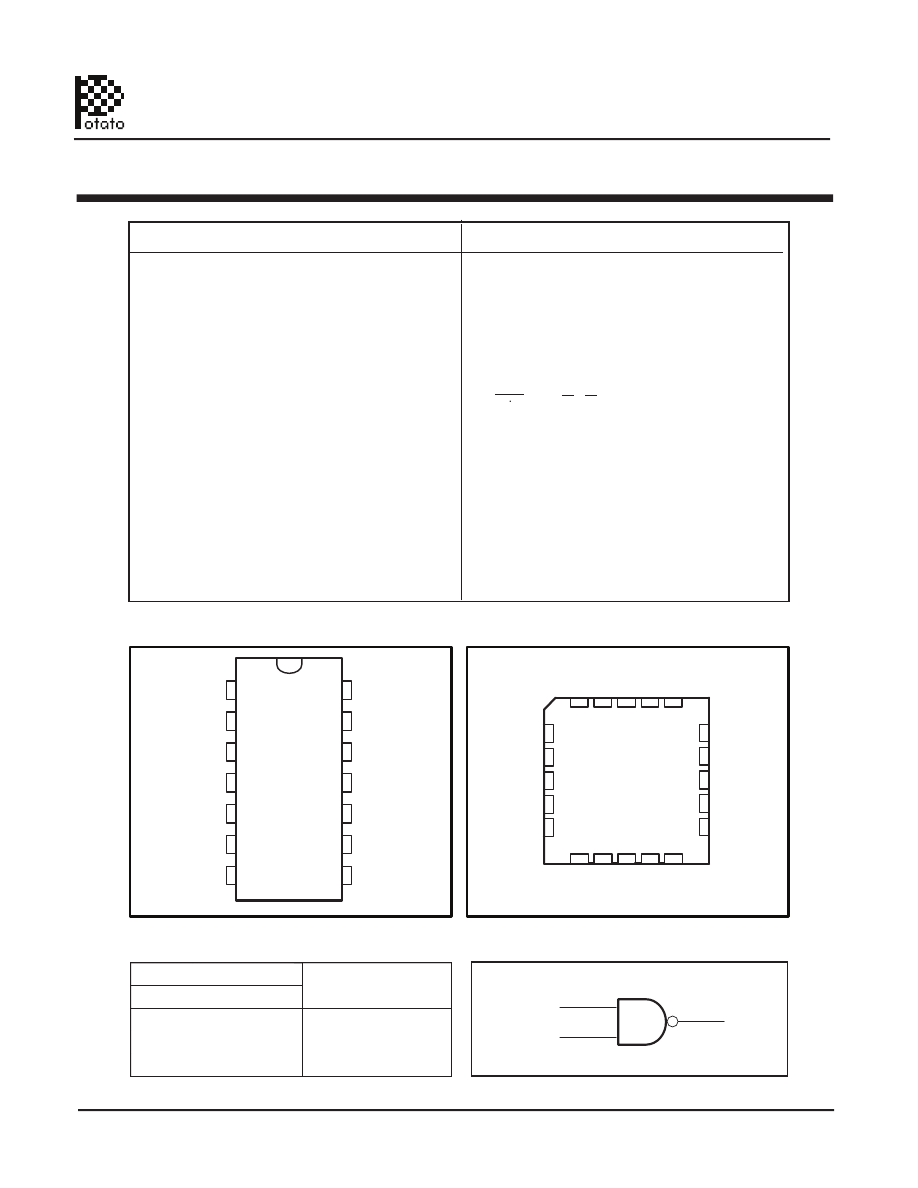

Pin Configuration

Logic Block Diagram

Pin Description

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1A

1B

1Y

2A

2B

2Y

GND

V CC

4B

4A

4Y

3B

3A

3Y

A

B

Y

DESCRIPTION:

Potato Semiconductor’s PO74G00A is designed for

world top performance using submicron CMOS

technology to achieve 1.125GHz TTL/CMOS output

frequency with less than 1.5ns propagation delay.

This quadruple 2-input positive-NAND gate is

designed for 1.65-V to 3.6-V V

CC

operation.

The PO74G00A performs the Boolean function

Y= A B or Y= A + B in positive logic.

Inputs can be driven from either 3.3V or 5V devices.

This feature allows the use of these devices as

translators in a mixed 3.3V/5V system environment.

3 2 1 20 19

9 10 11 12 13

4

5

6

7

8

18

17

16

15

14

4A

NC

4Y

NC

3B

1Y

NC

2A

NC

2B

1B 1A NC

3Y 3A

V

4B

2Y

GND

NC

CC

1

01/01/10

Potato Semiconductor Corporation

PO54G00A, PO74G00A

www.potatosemi.com