FEATURES:

. Patented technology

. Operating frequency up to 1.125GHz with 2pf load

. Operating frequency up to 550MHz with 5pf load

. Operating frequency up to 300MHz with 15pf load

. VCC Operates from 1.65V to 3.6V

. Propagation delay < 1.5ns max with 15pf load

. Low input capacitance: 4pf typical

. Available in 14pin 150mil wide SOIC package

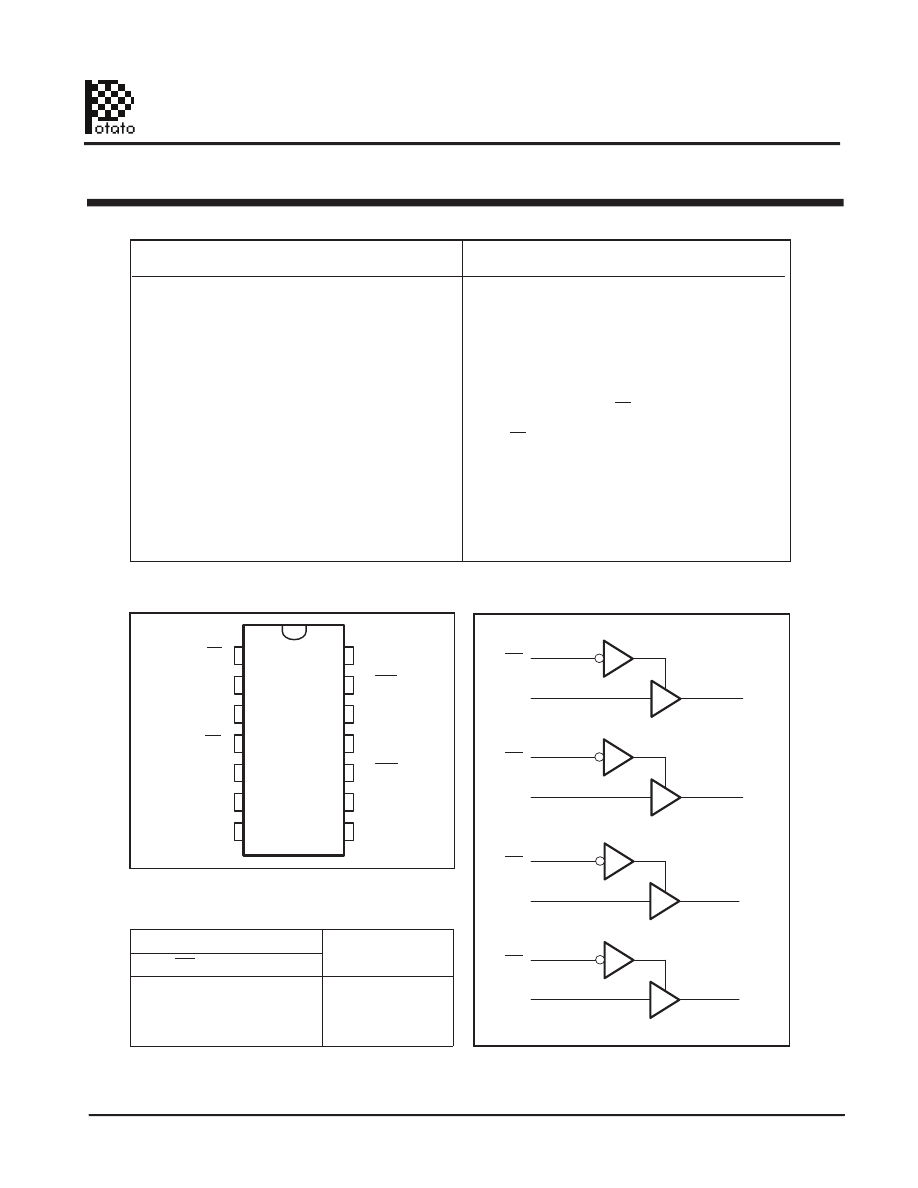

Pin Configuration

Logic Block Diagram

Pin Description

1

2

3

4

5

6

7

14

13

12

11

10

9

8

DESCRIPTION:

Potato Semiconductor’s PO74G125A is designed for

world top performance using submicron CMOS

technology to achieve 1.125GHz TTL /CMOS output

frequency with less than 1.5ns propagation delay.

This quadruple bus buffer gate is designed for 1.65-V

to 3.6-V V

CC

operation.

The

PO74G125A

features independent line drivers with

3-state outputs. Each output is disabled when the

associated output-enable (OE) input is high. To ensure

the high-impedance state during power up or power

down, OE should be tied to V

CC

through a pullup

resistor; the minimum value of the resistor is

determined by the current-sinking capability of

the driver.

Inputs can be driven from either 3.3V or 5V devices.

This feature allows the use of these devices as

translators in a mixed 3.3V/5V system environment.

1OE

1A

1Y

2OE

2A

2Y

GND

V

CC

4OE

4A

4Y

3OE

3A

3Y

INPUTS

OUTPUT

Y

OE

A

L

H

H

L

L

L

H

X

Z

10

3OE

9

3A

3Y

8

13

4OE

12

4A

4Y

11

1

1OE

2

1A

1Y

3

4

2OE

5

2A

2Y

6

74 Series Noise Cancellation GHz Logic

1

01/01/10

Potato Semiconductor Corporation

PO74G125A

www.potatosemi.com

QUADRUPLE BUS BUFFER GATES

WITH 3-STATE OUTPUTS