MAX II Product Backgrounder

Introduction

Building on nearly fifteen years of CPLD leadership and innovation, Altera introduces

the MAX

®

II family, the industry’s lowest-cost CPLDs. At half the cost of competing

CPLDs, MAX II devices are based on a new look-up table (LUT)-based

architecture that

delivers the lowest cost per I/O pin on the market and breaks new ground in CPLD

architectures. This instant-on, non-volatile device family targets general-purpose, low-

density logic applications, enabling designers to leverage the benefits of industry leading

CPLD devices in lieu of small ASICs and ASSPs, which are costlier and less flexible.

Built on a cost-optimized 0.18-µm flash process with six metal layers, MAX II devices

operate at approximately one-tenth the power of the previous-generation of MAX

devices. They offer densities ranging from 240 to 2,210 logic elements (LEs) (192 to

1,700 equivalent macrocells) and up to 272 user I/O pins. Table 1 describes some of the

highlights of MAX II devices, and Table 2 lists available packages.

MAX II Key Features

MAX II devices include many new features that take advantage of the technology

innovations that Altera’s legacy is built on. The device family was specifically designed

to reduce costs for both new and traditional CPLD applications.

Important MAX II features include:

•

One-tenth the Power Consumption of Prior CPLD Families

—The MAX II

devices have the lowest dynamic power in the industry, which results in the

lowest operating power consumption. For mission critical designs, MAX II

devices beat competing low-power products for battery life. Furthermore, the

MAX II family consumes one-tenth the power of the low-cost MAX 3000A

family.

•

Quadruple the Density

—The density range in macrocell equivalents is

approximately 192 to 1,700 macrocells. This quadruples what Altera offered in

previous families, and exceeds any offering from significant competitors today.

•

Twice the Performance

—The MAX II device family performance is on average

2X faster than the MAX 7000AE family as a result of improvements in routing

architecture, software algorithms, and process technology.

•

User Flash Memory

—Altera is the first programmable logic supplier to offer

user flash memory embedded within a programmable logic device (PLD). The

MAX II device family can therefore integrate commonly used serial or parallel

EEPROMs that typically range from 50 cents to $2.00 in volume, further reducing

the cost of end systems. The memory capacity per device is 8 Kbits across the

entire family.

•

Real-Time In-System Programmability (ISP)—

Users can reconfigure MAX II

devices in real time without interrupting functionality. This allows customers to

add functionality and flexibility to field-deployed customer systems.

For a complete description of the MAX II device feature set, please see the Altera

®

web

site at www.altera.com/max2.

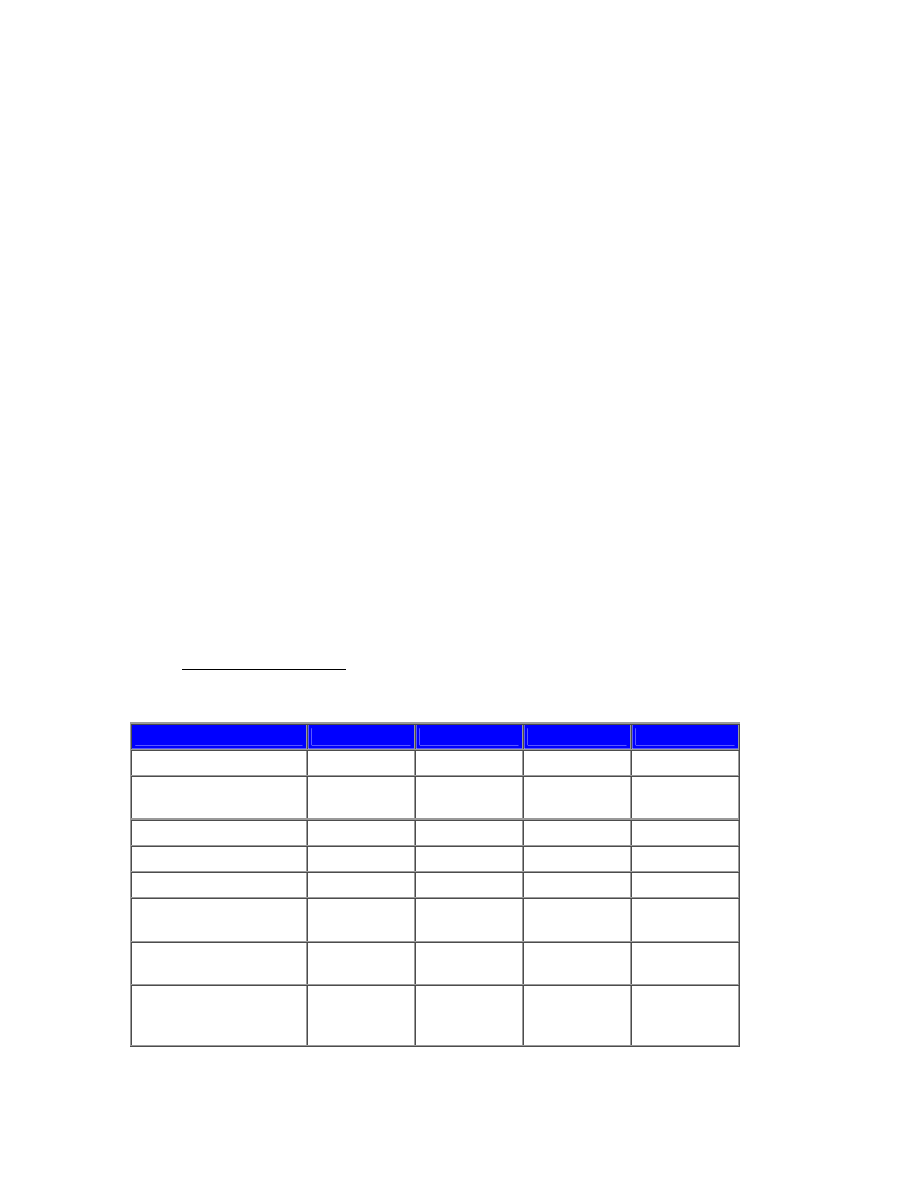

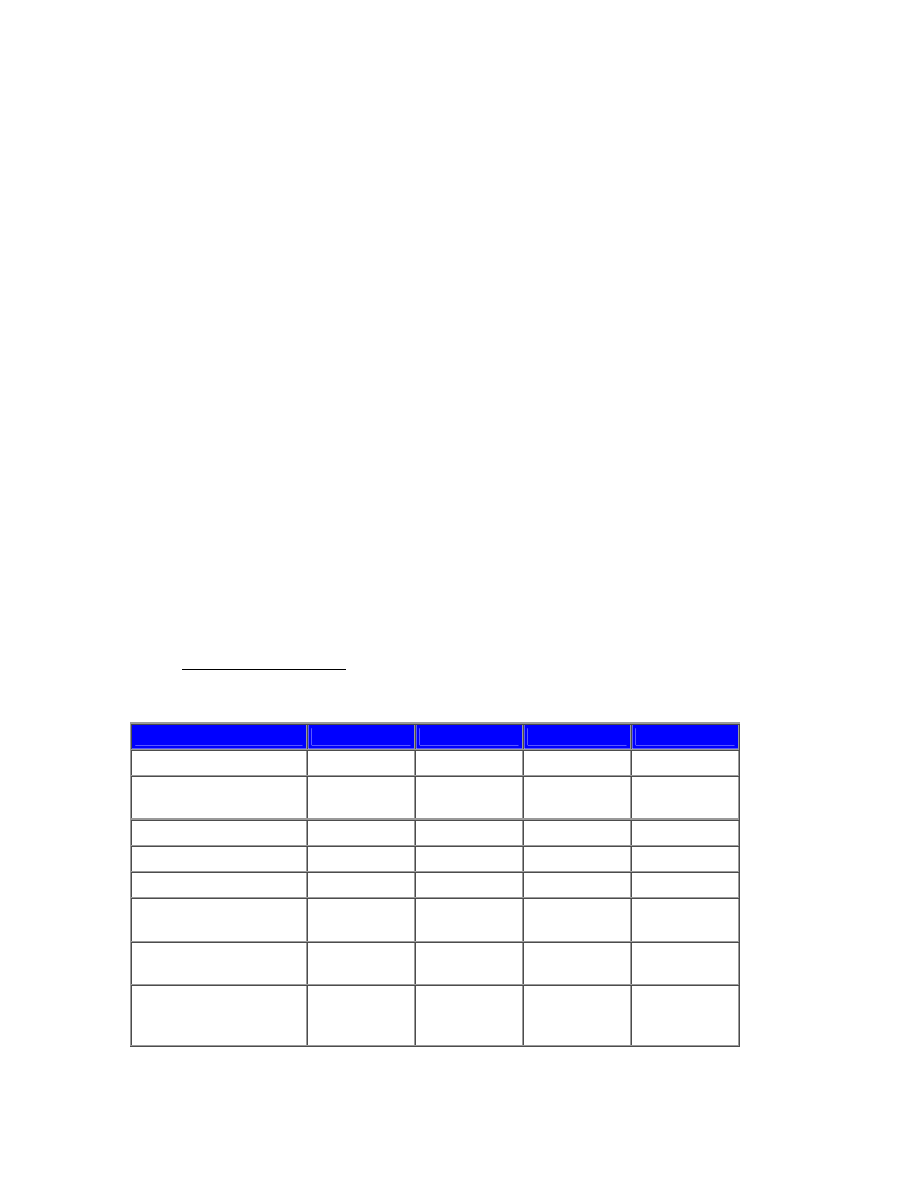

Table 1. Product Family Table

Feature

EPM240

EPM570

EPM1270

EPM2210

LEs

240

570

1,270

2,210

Typical Equivalent

Macrocells

192

440

980

1,700

Maximum User I/O Pins

80

160

212

272

User Flash Memory Bits

8,192

8,192

8,192

8,192

Speed Grades

3, 4, 5

3, 4, 5

3, 4, 5

3, 4, 5

t

pd1

Corner-to-Corner

Performance

(1)

(ns)

4.5

5.5

6.0

6.5

t

pd2

Fastest Performance

(ns)

3.6

3.6

3.6

3.6

Available Packages

(2)

100-pin

TQFP

(3)

100-pin TQFP

144-pin TQFP

256-pin BGA

(4)

144-pin TQFP

256-pin BGA

(4)

256-pin BGA

(4)

324-pin BGA

(4)

Notes:

(1) Correlates to the fastest commercial speed grade, which is a corner-to-corner delay path through the device.

(2) All packages support vertical migration across all densities.

(3) TQFP: thin quad flat pack.

(4) FineLine BGA® package (1.0-mm pitch).

Quartus II Design Software

MAX II devices are supported by Altera’s Quartus

®

II software, the highest-performance

and easiest-to-use design software available for CPLDs, FPGAs, and HardCopy™

devices. The Quartus II software now includes a MAX+PLUS

®

II look-and-feel option,

giving traditional MAX customers the full benefits of the Quartus II software without

having to learn a new user interface. Quartus II software also integrates seamlessly with

all of the leading third-party synthesis and simulation tools.

A free version of the software, Quartus II Web Edition, can be downloaded from the

Altera web site at www.altera.com.

Pricing, Packaging & Availability

The MAX II device family includes 4 members ranging in density from 240 to 2,210

logic elements. Low-cost packages are available for the MAX II devices, including 1.0-

mm FineLine BGA

®

(FBGA) and 0.5-mm thin quad flat pack (TQFP) packages.

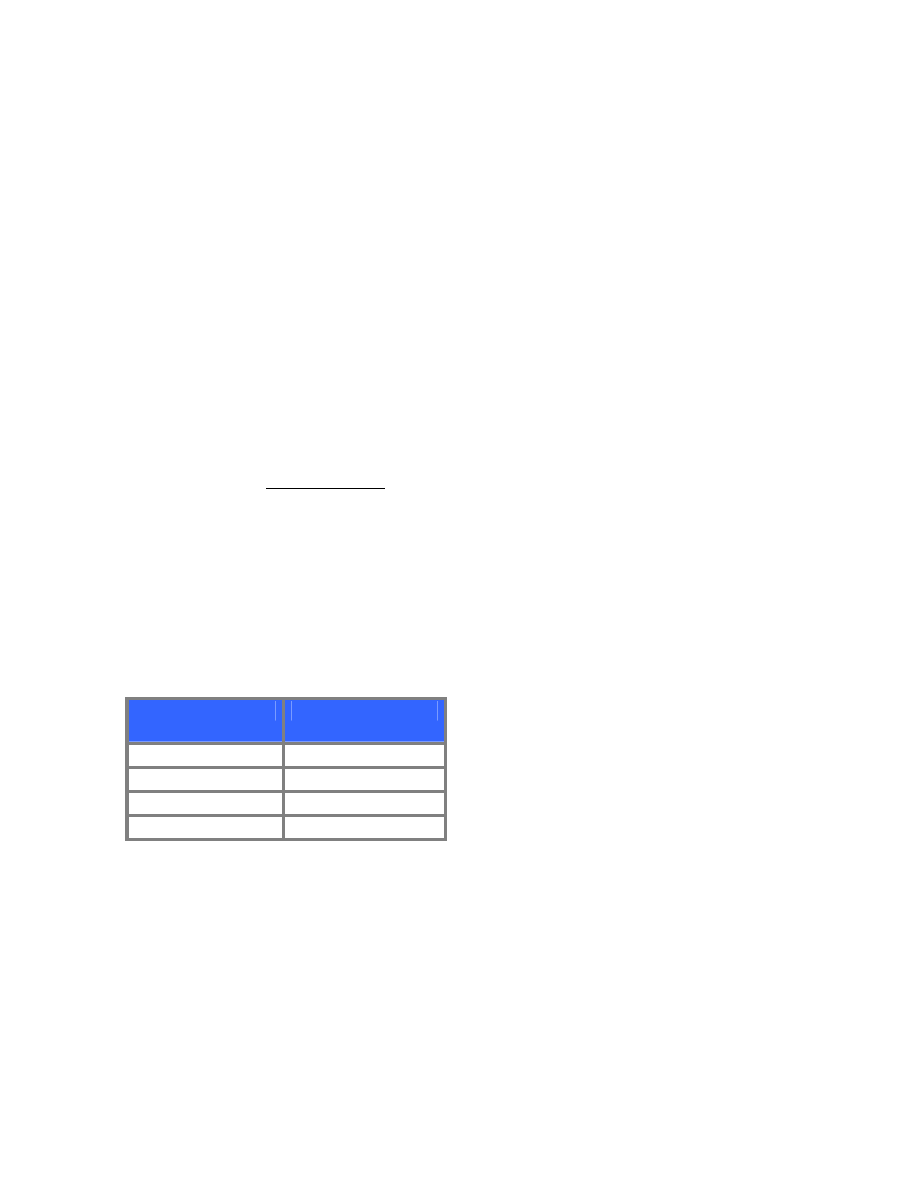

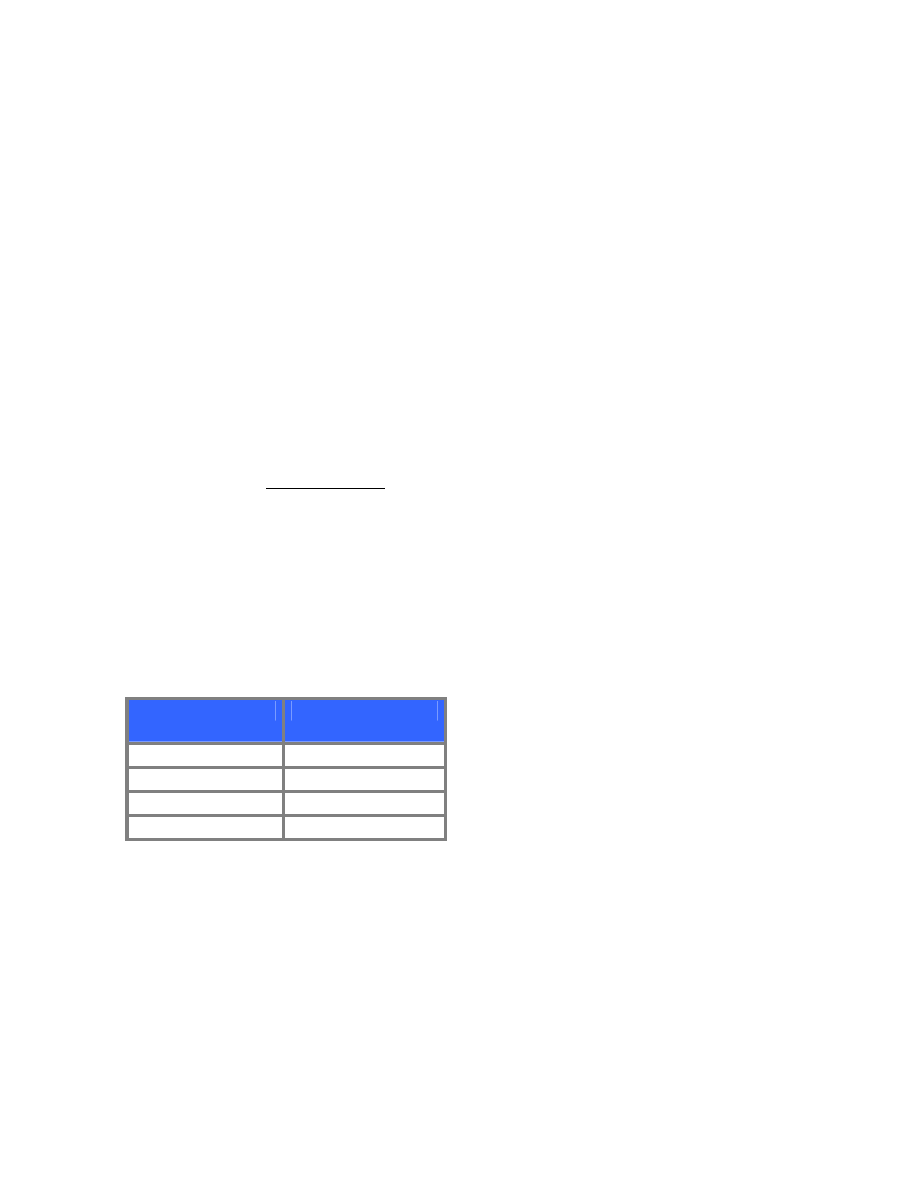

Table 2. Pricing Table

Device

Price 1

(1)

EPM240

$1.50

EPM570

$2.30

EPM1270

$4.25

EPM2210

$7.00

(1)

Resale price based on 500K unit volumes in 2005